In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branch instruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch is taken. The instruction in the load delay slot cannot use the data loaded by the load instruction. The load delay slot can be filled with an instruction that is not dependent on the load; a nop is substituted if such an instruction cannot be found. MIPS I has instructions to perform addition and subtraction.

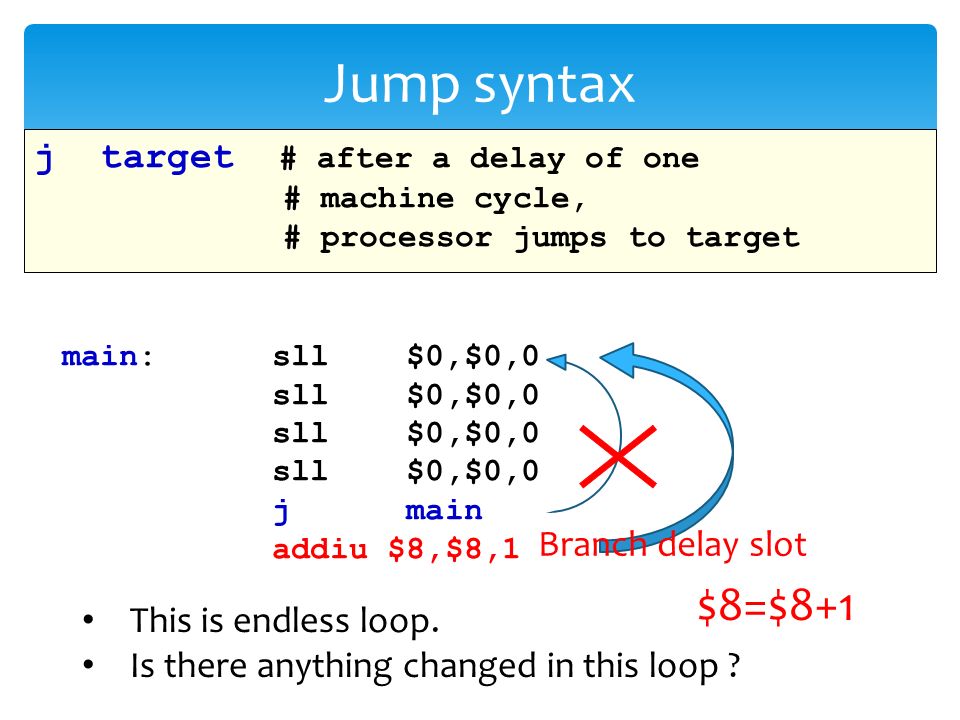

There are many methods to deal with the pipeline stalls caused by branchdelay. We discuss fourControl/branching hazard: delay between fetching control flow instruction (branch or jump) and actual jump. For that reason MIPS introduced branch delay slot. MIPS has simplified branch testing (rx ry, rx!= ry, rx 0, rx!= 0), the branch condition evaluation and branch target address calculation BOTH happen in instruction decode (ID) stage. In MIPS, executing a branch in a branch delay slot results in UNDETERMINED behavior. Conditional delay slot instructions. Things get more complicated when the delay-slot instruction is effectively predicated on the branch direction. SPARC supports 'annulled' branches in which the delay-slot instruction is not executed if the branch is not taken. More problems with delay. There are some MIPS instructions that do not immediately produce a result. One of these is the jump (j spin) instruction near the end of your program. It does not jump immediately, but always execute one more instruction in a delay slot before transferring to its target.

simple compile-time schemes in whichpredictions are static - they are fixed for each branch during the entireexecution, and the predictions are compile-time guesses.Stallpipeline

Predicttaken

Predictnot taken

Delayedbranch

Stall pipeline

The simplest scheme to handle branches is to freezeor flush the pipeline, holdingor deleting any instructions after the branch until the branch destinationis known.

Advantage: simple both to software and hardware (solutiondescribed earlier)

Predict Not Taken

A higher performance, and only slightly more complex, scheme is to predictthe branch as not taken, simply allowing the hardware to continueas if the branch were not executed. Care must be taken notto change the machine state until the branch outcome is definitely known.

The complexity arises from:

wehave to know when the state might be changed by an instruction;

wehave to know how to 'back out' a change.

The pipeline with this scheme implemented behaves as shown below:

| UntakenBranch Instr | IF | ID | EX | MEM | WB |

| Instr i+1 | IF | ID | EX | MEM | WB |

| Instr i+2 | IF | ID | EX | MEM | WB |

| TakenBranch Instr | IF | ID | EX | MEM | WB |

| Instr i+1 | IF | idle | idle | idle | idle |

| Branch target | IF | ID | EX | MEM | WB |

| Branch target+1 | IF | ID | EX | MEM | WB |

Predict Taken

An alternative scheme is to predict the branch as taken. As soon asthe branch is decoded and the target address is computed, we assume thebranch to be taken and begin fetching and executingat the target address.

Because in DLX pipeline the target address is not known any earlier than the branch outcome, there is no advantage in this approach.In some machines where the target address is known before the branchoutcome a predict-taken scheme might make sense.

Delayed Branch

In a delayed branch, the execution cycle with a branch delay of lengthn is

Branch instrSequential successors are in the branch-delayslots. These instructions are executed whether or not thebranch is taken.The pipeline behavior of the DLX pipeline, which has one branch delayslot is shown below:

sequential successor 1

sequential successor 2

. . . . .

sequential successor n

Branch target if taken

| Untakenbranch instr | IF | ID | EX | MEM | WB |

| Branch delay instr(i+1) | IF | ID | EX | MEM | WB |

| Instr i+2 | IF | ID | EX | MEM | WB |

| Instr i+3 | IF | ID | EX | MEM | WB |

| Instr i+4 | IF | ID | EX | MEM | WB |

| Takenbranch instr | IF | ID | Branch delay instr(i+1) | IF | ID | EX | MEM | WB |

| Branch target | IF | ID | EX | MEM | WB | |||

| Branch target+1 | IF | ID | EX | MEM | WB | |||

| Branch target+2 | IF | ID | EX | MEM | WB |

The job of the compiler is to make the successor instructions validand useful.

We will show three branch-scheduling schemes:

Frombefore branchrestrictions on the instructionsthat are scheduled into the delay slots and

Fromtarget

Fromfall through

ourability to predictat compile time whether a branch is likely to be taken ornot.

CancellingBranch

To improve the ability of the compiler to fill branch delay slots, mostmachines with conditional branches have introduced a cancellingbranch. In a cancelling branch the instruction includesthe direction that the branch was predicted.Delay Slot Instruction Mips Helmet

- if the branch behaves as predicted, the instruction in the branchdelay slot is fully executed;

- if the branch is incorrectly predicted, the instruction in the delayslot is turned into no-op(idle).

Delay Slot Instruction Mips Software

The behavior of a

| Untakenbranch instr | IF | ID | EX | MEM | WB |

| Branch delay instr(i+1) | IF | ID | idle | idle | idle |

| Instr i+2 | IF | ID | EX | MEM | WB |

| Instr i+3 | IF | ID | EX | MEM | WB |

| Instr i+4 | IF | ID | EX | MEM | WB |

| Takenbranch instr | IF | ID | Branch delay instr(i+1) | IF | ID | EX | MEM | WB |

| Branch target | IF | ID | EX | MEM | WB | |||

| Branch target+1 | IF | ID | EX | MEM | WB | |||

| Branch target+2 | IF | ID | EX | MEM | WB |

The advantage of cancellingbranches is that they eliminate the requirements on theinstructionplaced in the delay slot.

Delayed branches are an architecturallyvisible feature of the pipeline. This is the source both of their advantage- allowing the use of simple compiler scheduling to reduce branch penalties;and

their disadvantage - exposingan aspect of the implementation that is likely to change.

In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branchinstruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch is taken. Thus, by design, the instructions appear to execute in an illogical or incorrect order. It is typical for assemblers to automatically reorder instructions by default, hiding the awkwardness from assembly developers and compilers.

Branch delay slots[edit]

When a branch instruction is involved, the location of the following delay slot instruction in the pipeline may be called a branch delay slot. Branch delay slots are found mainly in DSP architectures and older RISC architectures. MIPS, PA-RISC, ETRAX CRIS, SuperH, and SPARC are RISC architectures that each have a single branch delay slot; PowerPC, ARM, Alpha, and RISC-V do not have any. DSP architectures that each have a single branch delay slot include the VS DSP, μPD77230 and TMS320C3x. The SHARC DSP and MIPS-X use a double branch delay slot; such a processor will execute a pair of instructions following a branch instruction before the branch takes effect. The TMS320C4x uses a triple branch delay slot.

The following example shows delayed branches in assembly language for the SHARC DSP including a pair after the RTS instruction. Registers R0 through R9 are cleared to zero in order by number (the register cleared after R6 is R7, not R9). No instruction executes more than once.

The goal of a pipelined architecture is to complete an instruction every clock cycle. To maintain this rate, the pipeline must be full of instructions at all times. The branch delay slot is a side effect of pipelined architectures due to the branch hazard, i.e. the fact that the branch would not be resolved until the instruction has worked its way through the pipeline. A simple design would insert stalls into the pipeline after a branch instruction until the new branch target address is computed and loaded into the program counter. Each cycle where a stall is inserted is considered one branch delay slot. A more sophisticated design would execute program instructions that are not dependent on the result of the branch instruction. This optimization can be performed in software at compile time by moving instructions into branch delay slots in the in-memory instruction stream, if the hardware supports this. Another side effect is that special handling is needed when managing breakpoints on instructions as well as stepping while debugging within branch delay slot.

The ideal number of branch delay slots in a particular pipeline implementation is dictated by the number of pipeline stages, the presence of register forwarding, what stage of the pipeline the branch conditions are computed, whether or not a branch target buffer (BTB) is used and many other factors. Software compatibility requirements dictate that an architecture may not change the number of delay slots from one generation to the next. This inevitably requires that newer hardware implementations contain extra hardware to ensure that the architectural behavior is followed despite no longer being relevant.

Load delay slot[edit]

Delay Slot Instruction Mips Bike Helmet

A load delay slot is an instruction which executes immediately after a load (of a register from memory) but does not see, and need not wait for, the result of the load. Load delay slots are very uncommon because load delays are highly unpredictable on modern hardware. A load may be satisfied from RAM or from a cache, and may be slowed by resource contention. Load delays were seen on very early RISC processor designs. The MIPS I ISA (implemented in the R2000 and R3000 microprocessors) suffers from this problem.

The following example is MIPS I assembly code, showing both a load delay slot and a branch delay slot. Casino summerside.

See also[edit]

External links[edit]

Frombefore branchrestrictions on the instructionsthat are scheduled into the delay slots and

Fromtarget

Fromfall through

ourability to predictat compile time whether a branch is likely to be taken ornot.

CancellingBranch

To improve the ability of the compiler to fill branch delay slots, mostmachines with conditional branches have introduced a cancellingbranch. In a cancelling branch the instruction includesthe direction that the branch was predicted.Delay Slot Instruction Mips Helmet

- if the branch behaves as predicted, the instruction in the branchdelay slot is fully executed;

- if the branch is incorrectly predicted, the instruction in the delayslot is turned into no-op(idle).

Delay Slot Instruction Mips Software

The behavior of a predicted-taken cancellingbranch depends on whether the branch is taken or not:| Untakenbranch instr | IF | ID | EX | MEM | WB |

| Branch delay instr(i+1) | IF | ID | idle | idle | idle |

| Instr i+2 | IF | ID | EX | MEM | WB |

| Instr i+3 | IF | ID | EX | MEM | WB |

| Instr i+4 | IF | ID | EX | MEM | WB |

| Takenbranch instr | IF | ID | Branch delay instr(i+1) | IF | ID | EX | MEM | WB |

| Branch target | IF | ID | EX | MEM | WB | |||

| Branch target+1 | IF | ID | EX | MEM | WB | |||

| Branch target+2 | IF | ID | EX | MEM | WB |

The advantage of cancellingbranches is that they eliminate the requirements on theinstructionplaced in the delay slot.

Delayed branches are an architecturallyvisible feature of the pipeline. This is the source both of their advantage- allowing the use of simple compiler scheduling to reduce branch penalties;and

their disadvantage - exposingan aspect of the implementation that is likely to change.

In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branchinstruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch is taken. Thus, by design, the instructions appear to execute in an illogical or incorrect order. It is typical for assemblers to automatically reorder instructions by default, hiding the awkwardness from assembly developers and compilers.

Branch delay slots[edit]

When a branch instruction is involved, the location of the following delay slot instruction in the pipeline may be called a branch delay slot. Branch delay slots are found mainly in DSP architectures and older RISC architectures. MIPS, PA-RISC, ETRAX CRIS, SuperH, and SPARC are RISC architectures that each have a single branch delay slot; PowerPC, ARM, Alpha, and RISC-V do not have any. DSP architectures that each have a single branch delay slot include the VS DSP, μPD77230 and TMS320C3x. The SHARC DSP and MIPS-X use a double branch delay slot; such a processor will execute a pair of instructions following a branch instruction before the branch takes effect. The TMS320C4x uses a triple branch delay slot.

The following example shows delayed branches in assembly language for the SHARC DSP including a pair after the RTS instruction. Registers R0 through R9 are cleared to zero in order by number (the register cleared after R6 is R7, not R9). No instruction executes more than once.

The goal of a pipelined architecture is to complete an instruction every clock cycle. To maintain this rate, the pipeline must be full of instructions at all times. The branch delay slot is a side effect of pipelined architectures due to the branch hazard, i.e. the fact that the branch would not be resolved until the instruction has worked its way through the pipeline. A simple design would insert stalls into the pipeline after a branch instruction until the new branch target address is computed and loaded into the program counter. Each cycle where a stall is inserted is considered one branch delay slot. A more sophisticated design would execute program instructions that are not dependent on the result of the branch instruction. This optimization can be performed in software at compile time by moving instructions into branch delay slots in the in-memory instruction stream, if the hardware supports this. Another side effect is that special handling is needed when managing breakpoints on instructions as well as stepping while debugging within branch delay slot.

The ideal number of branch delay slots in a particular pipeline implementation is dictated by the number of pipeline stages, the presence of register forwarding, what stage of the pipeline the branch conditions are computed, whether or not a branch target buffer (BTB) is used and many other factors. Software compatibility requirements dictate that an architecture may not change the number of delay slots from one generation to the next. This inevitably requires that newer hardware implementations contain extra hardware to ensure that the architectural behavior is followed despite no longer being relevant.

Load delay slot[edit]

Delay Slot Instruction Mips Bike Helmet

A load delay slot is an instruction which executes immediately after a load (of a register from memory) but does not see, and need not wait for, the result of the load. Load delay slots are very uncommon because load delays are highly unpredictable on modern hardware. A load may be satisfied from RAM or from a cache, and may be slowed by resource contention. Load delays were seen on very early RISC processor designs. The MIPS I ISA (implemented in the R2000 and R3000 microprocessors) suffers from this problem.

The following example is MIPS I assembly code, showing both a load delay slot and a branch delay slot. Casino summerside.